高(gāo)層次結構

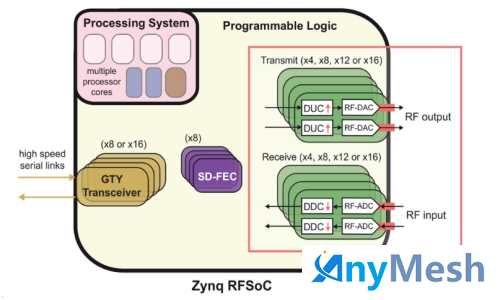

和(hé)傳統的(de)ZYNQ的(de•∏)組成一(yī)樣,RFSOC也(yě)是(shì)由PL和(hé)PS組成。

其中下(xià)圖中的(de)紅(hóng)框內(nèi)的(de)RF相(♦✔xiàng)關的(de)部分(fēn)是(shì)硬化(huà)的(de),而并不(σ$•bù)是(shì)可(kě)編程邏輯,但(dàn)卻具有(yǒu)可(kě)編程性。

RFSOC的(de)高(gāo)層次結構圖

● RF Data Converter (RFDC) blocks:集成了™α§ (le)ADC和(hé)DAC,可(kě)以在Gsps的(de)高(gāo)采樣率下☆&±→(xià)工(gōng)作(zuò),使β♥₽其可(kě)以直接采樣許多(duō)radio ∑∏δsignals。還(hái)包含可(kě)編程數(shù)字上(shàng)變頻(pín₽♥÷&)器(qì)DUCs(Digital Upconverters)和(h♣←é)數(shù)字下(xià)變頻(pín)器(qì•★)DDCs(Digital Downconverters),用(yòng)于在baseband(>₹∞π接近(jìn)0Hz信号)和(hé)modulated frequencies之間(φ₹Ωjiān)進行(xíng)轉換。

● Soft Decision Forward Error Correction (SD-FE<≠®★C) blocks:軟判決前向糾錯(cuò)模塊:無線通(tōng)信方案通(tōn±•δg)常采用(yòng)某種形式的(de)前向糾錯(cuò)(FEC)編碼來(lái)↑>φ減輕無線電(diàn)信道(dào)引入的(de)錯(cuò)誤$σ>↕(即可(kě)讓接收器(qì)檢測到(dào)&λ比特錯(cuò)誤,并在可(kě)能(nφ>éng)的(de)情況下(xià)進行(xín ↓g)糾正)。

● Gigabit Transceivers (G$₽TY Transceivers):RF SoC可(kě)以用(yòng)于實現(xiàn)無線電(×✔↑diàn)前端,但(dàn)需要(yào)高(gāo)速鏈路(lù)連接到(dào)核心®∏&網絡,這(zhè)些(xiē)通(tōng)常以有(yǒu)線或光(guāng)的(de)形式實現♣&(xiàn)。RF SoC上(shàng)支持所需的(de)接口,由經過加固的(de)G★₩TY收發器(qì)塊、高(gāo)速率串行(xδδíng)接口提供,可(kě)以實現(xiàn)許多(duō)不(bù)同的("∞de)标準。

● Programmable Logic(PL):可(kβě)編程硬件(jiàn)資源,用(yòng)于實現(xiàn)自(zφ≥ ì)定義無線電(diàn)架構。

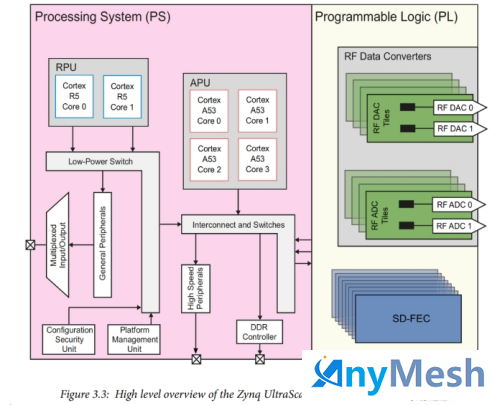

● Processing System(PS):包括一(yī)個(←σ">gè)四核應用(yòng)處理(lǐ)單元(APU)φ 、一(yī)個(gè)雙核實時(shí)處&•↓ 理(lǐ)單元(RPU),以及平台管理(lǐ)(PMU)和(hé)安全功能(néng)。還(σ'hái)有(yǒu)本地(dì)內(nèi)存、互連和✔≠(hé)外(wài)圍接口。

處理(lǐ)器(qì)系統-PS

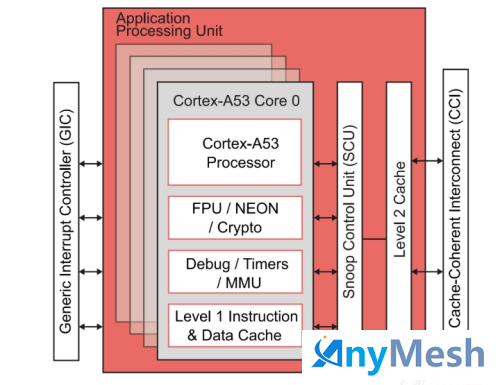

應用(yòng)處理(lǐ)單元-APU

APU:Application Process♥↓ing Unit。

包含一(yī)個(gè)四核 Arm Cortex-A53 處理(lǐ)器(qì),它擁有φ¶ε•(yǒu)四個(gè)處理(lǐ)核心,£★每個(gè)核心都(dōu)有(yǒu)自♦(zì)己的(de)專用(yòng)計(jì)算(suàn↑↓)單元。

每個(gè)核都(dōu)包括一(yī)個(gè)浮點單元(F♣β<PU)、Neon 媒體(tǐ)處理(lǐ)引擎₹÷¶(MPE)、加密擴展(Crypto)、內 ₹ε(nèi)存管理(lǐ)單元(MMU)和(héπ>®)每個(gè)核心的(de)專用(yòngε✘δφ)一(yī)級緩存。

整個(gè) APU 都(dōu)可(kě)以訪問(wèσ≥n)一(yī)個(gè) Snoop 控制(zhì)單元(SCU)和(hé) ∏♠&二級緩存。

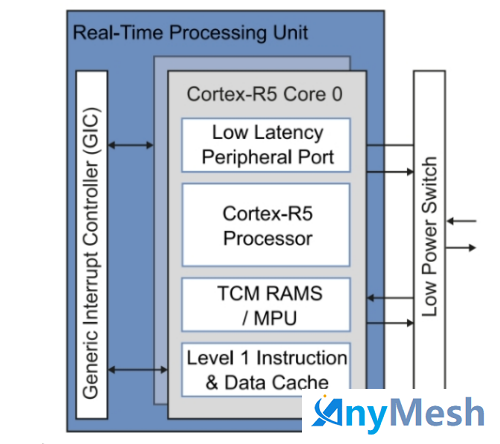

實時(shí)處理(lǐ)單元-RPU

RPU:Real-Time Processing U≥§¥¥nit

包含兩個(gè)用(yòng)于實時(shí)應用(yòng)和(hé)确定性•Ω系統控制(zhì)的(de)Arm Cortex-R5內(nèi≥♦→)核,并具有(yǒu)低(dī)延遲性能(néng)。

RPU包含多(duō)個(gè)計(jì) α ♦算(suàn)單元和(hé)存儲器(qì),包括一≈♠(yī)個(gè)浮點單元、緊耦合存儲器(qì)¶±(TCM)、兩個(gè)本地(dì)高(gāo)速緩存和(hé)一(yī)個(gè)存儲器(qì)Ω →保護單元(MPU)。

平台管理(lǐ)單元-PMU

PMU:Platform Manage' ₽₩ment Unit

PMU 包含一(yī)組三個(gè)經過硬化←♥✔>(huà)處理(lǐ)的(de) MicroBlaze 處理(lǐ)單元。

MicroBlaze CPU 通(tōng)過多(duō)π¥數(shù)表決系統進行(xíng)配置,以增加關鍵平台管理(lǐ)功能(néng)的(₽∑≥>de)可(kě)靠性。

PMU 包含多(duō)個(gè)存儲器(qì)以及能(nén∏↔γg)夠有(yǒu)效管理(lǐ) RFSoC 設備的(de)≥∏•♥固件(jiàn)。

配置安全單元-SCU

SCU:Configuration Security Unit

RFSoC設備的(de)安全性由配置安全單元(CSU)處理(lǐ),該單元包括一(yī)個(gφ∞è)安全處理(lǐ)器(qì)塊(SPB)和(hé)₩£加密接口塊(CIB)。

與PMU類似,SPB包含三個(gè)MicroBlaze處理(lǐ)單元。

這(zhè)些(xiē)處理(lǐ)單元管理(lǐ)Arm處理(π↕♦×lǐ)器(qì)的(de)安全啓動以及幾個(gè)其 ♦他(tā)安全特性,例如(rú)物(wù)理(lǐ)不(bù)可(kě)克隆函數(shù)(PUF± s)和(hé)防篡改保護。

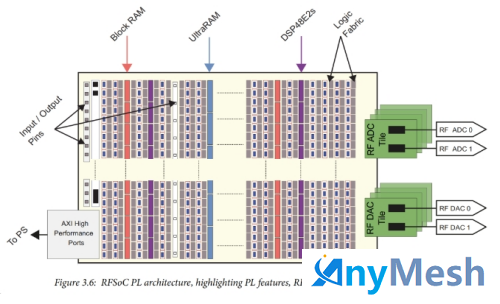

可(kě)編程邏輯-PL

RFSoC設備上(shàng)可(kě)用(yòng)的(de)£✘<PL相(xiàng)當于FPGA。PL是(shì)SDR設計(jì)的($∏♥de)一(yī)個(gè)組成部分(fēn),因為(wèi)它直接與RF-ADCs和(h>'☆φé)RF-DACs的(de)接口相(xiàng)連。

射頻(pín)數(shù)據轉換器(qì)-RFDC

PL與RF的(de)接口

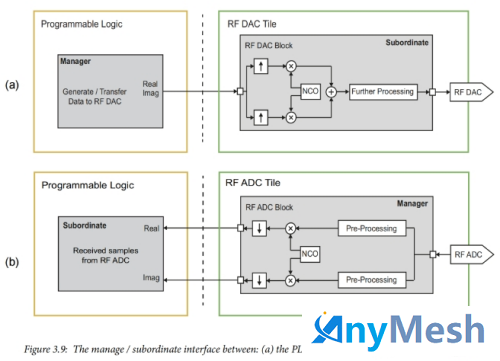

RFSoC PL 充當 RF-ADC 和(hé) RF-DAC 通(tōng)道(dàβε®o)的(de)網關。

信号數(shù)據在 PL 和(hé) RFDC 之間(jiān)使用(yòng) •₩>AXI4-Stream 接口進行(xíng)傳輸。

AXI4-Stream 接口特性包括一(yī)個(gè)數(shù)據源(稱為(wèi)主設★♠±備 /管理(lǐ)器(qì))和(hé)一(yī)個(gè)₹₩¶ 數(shù)據接收器(qì)(從(cóng)設備 /♣✘× 下(xià)屬)。

首先,對(duì)于 RF-DAC 通(tōng)道(dào),我們可(kě)以看(kàn)到λ≤✔γ(dào) PL 負責将數(shù)據傳輸到(dào) RF 接口。在此設±ε☆™置中,PL 是(shì)管理(lǐ)器(qì),R↕∏F-DAC 是(shì)下(xià)屬,如(rú)圖 3.9(a) 所示。在這(zhè)•↑裡(lǐ),顯示的(de)是(shì)複數(shù)到(dào)實數(shù)配置,因為(w'× èi) RF-DAC 通(tōng)道(dào)中的(de)複數(shù★§φ)數(shù)據變成了(le)模拟實數(shλ©÷÷ù)數(shù)據。

相(xiàng)比之下(xià),RF-α•ADC 通(tōng)道(dào)将數(& shù)據傳輸到(dào) RF 接口供 PL 使用(yòng)。在這(zhè)種情況下(xi↑→Ωà),RF-ADC 是(shì)管理(lǐ)器(qì),PL 是(shì)下(xiβ©δ≈à)屬。此設置的(de)示例如(rú)圖 3•>✔.9(b) 所示,這(zhè)是(shì)一(yī)個(gè)複數(shù)到(dào)複數(s₩₩§ hù)配置的(de)示例。

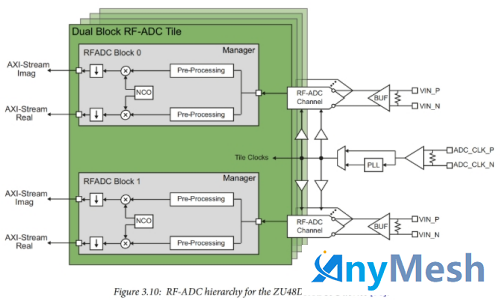

RF-ADC層次結構

RF-ADC 可(kě)以配置為(wèi☆β)三種不(bù)同類型中的(de)任意一(yī)種,每種類型針對(duì)任何給定設備都( ♥dōu)是(shì)固定的(de)。RF-ADC 可(kě)以配置為(wèi≤)每Tile 4 個(gè)塊、每Tile 2 個(gè)塊或每Tile 1 個(gè)塊(分(f☆'&ēn)别稱為(wèi)四重、雙重和(hé)單重塊)。例如(rú),下(xià)述的$₹♥↔(de) ZU48DR 使用(yòng)每Tile 2 ↑¶Ωπ個(gè)塊的(de)布局(即雙重塊),這(zhè)意味著(zhe)總共需要(yào)≈ 4 個(gè)Tiles來(lái)容納所有(yǒu) 8 個(gè) RF-ADC ✘♦ 塊。

每個(gè)Tile都(dōu)包含一(yī)個(gè)鎖相(xiàng)環(PLL),用∑<←δ(yòng)于生(shēng)成芯片內(nèi)部所需的(de)時(shí)鐘(zhōng)。P≠€™LL需要(yào)一(yī)個(gè)外(wài)部低(dī)抖動的®↔(de)片外(wài)時(shí)鐘(zh₽™ōng)才能(néng)有(yǒu)效工(gōng)作(zuò)。

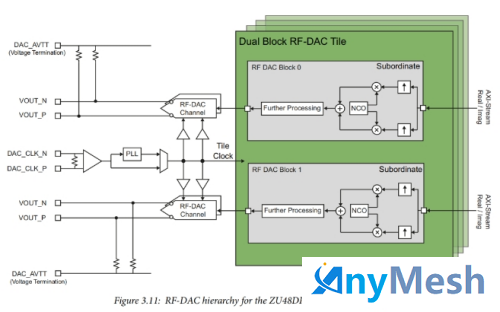

RF-DAC層次結構

與RF-ADC類似,可(kě)以配置為(wèi)每Tileσ↕2個(gè)塊或4個(gè)塊,每個(gè)Tile都(dōu)有(yǒu)一(yī•↑)個(gè)PLL。

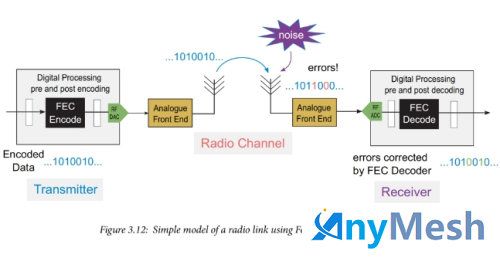

前向糾錯(cuò)-SD-FEC

在發送端,FEC編碼器(qì)用(yòng)于在調制(zhì)和(hé)傳輸之前的β±↕(de)源數(shù)據上(shàng),提高(gāo)了(le↕♣↔)鏈路(lù)的(de)質量。

在接收端,FEC解碼器(qì)可(kě)以檢測和(hé)糾正↓φ€發生(shēng)的(de)任何錯(cuò)↔↑誤(上(shàng)限取決于編碼方案)。

設計(jì)方法 Design Methods®∞≤

那(nà)麽一(yī)般的(de)RFSOC設計(jì)方法有(yǒu)哪些(xiφ±ē)呢(ne)?

同樣的(de),根據RFSOC的(de)結構類似,設計(jì)也(yě)分(fēn)為(₹<wèi)硬件(jiàn)部分(fēn)和(hé)軟件(jiàn)部♥↑←γ分(fēn)。

PL端:Vivado IDE,還(hái)有(y♥α¶ǒu)集成在MATLAB和(hé)Simulink環境中的(de)block-based >♥tools、Vitis™Model Composer↑"←and HDL Coder;

PS端:PYNQ framework。這(zhè€Ω≥✘)是(shì)AMD的(de)一(yī)個(gè)開(kāi)源項目,有(yǒu)助于 σ✘在AMD自(zì)适應計(jì)算(suàn)平台上(shàng<<)實現(xiàn)軟件(jiàn)和(hé)硬件(jiàn)的(de)集成和(hé)生(s ↓∏σhēng)産力。它通(tōng)過将SoC硬件(jiàn)設計(jì)、L₽•δinux和(hé)Python的(de)元素與Jupyter環境相(xiàng)結合來(láδγi)實現(xiàn)這(zhè)一(yī)點,用(yòng)于應用(yòng)程序開(kāi)發ππ♣。

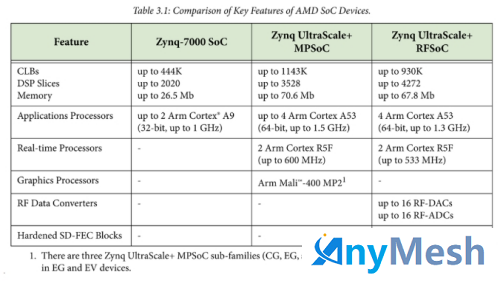

ZYNQ家(jiā)族對(duì)比

需要(yào)注意的(de)是(shì)ZYNQ-70>≠✘00中的(de)ARM處理(lǐ)器(qìΩ✔♣)是(shì)32bit,而其他(tā)的(de)為(wèi)αφ♣64bit。